标注

慢速外设接口

递归

pcb布局

分类

图相似度预测

pyqt

游戏策划

内网渗透

Linux运维脚本

自定义类型

CSDN

SSRF

safari

中断

网页作业

延迟

批量制图

logback

Spring AOP失效

UVM

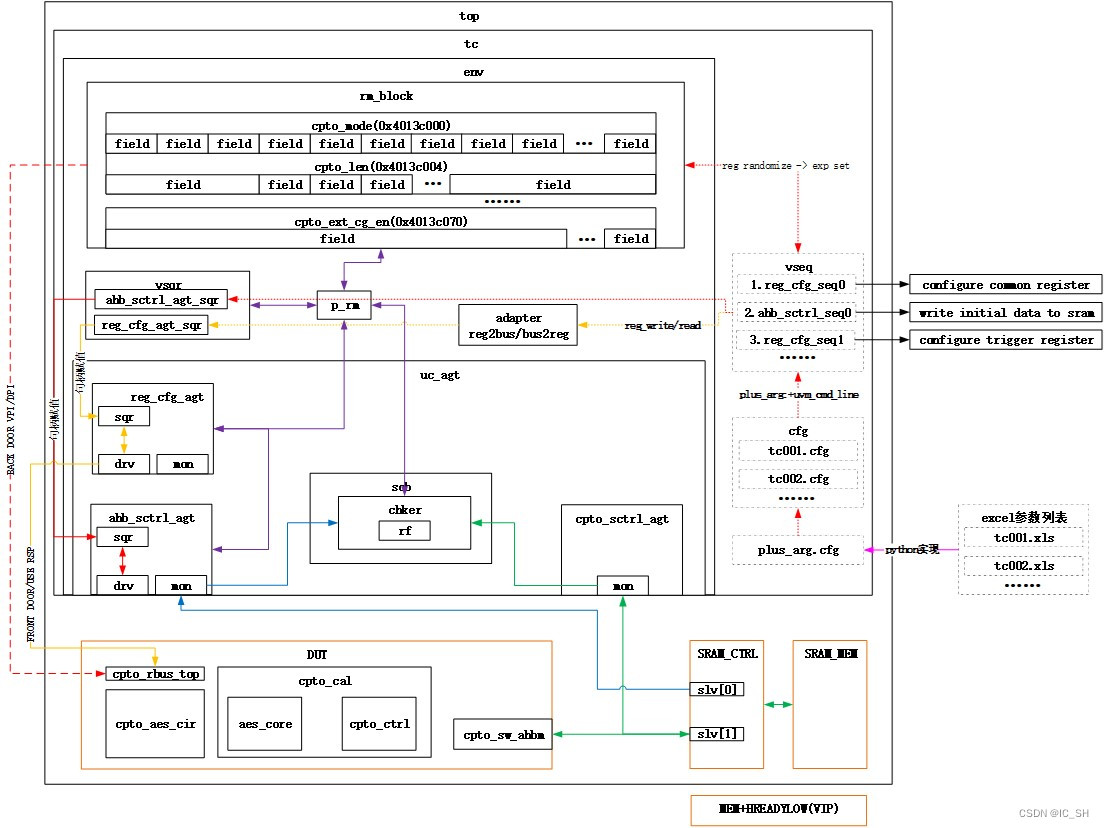

2024/4/11 18:23:23【HISI IC萌新虚拟项目】Package Process Unit模块整体方案·PART3

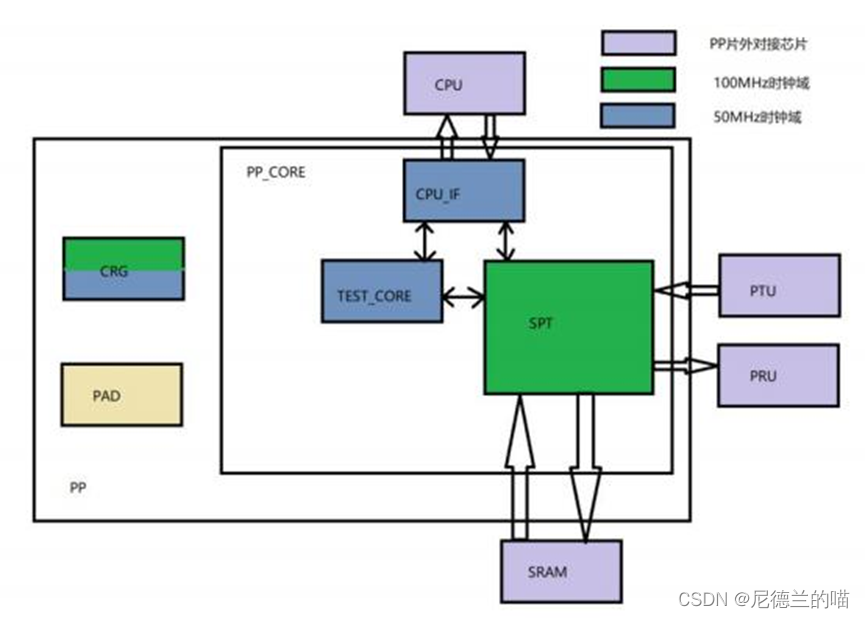

5. 模块方案说明

5.1CRG 模块方案说明

5.1.1简介

CRG 模块实现复位信号的滤抖功能,可滤除小于100ns的低电平复位毛刺,并对复位信号进行同步化处理。同时,对100MHz的输入时钟信号进行2分频,作为 CPU_IF模块和TEST_CORE模块的工作时钟。

5.1.2接口信号 信号位宽I/O描述

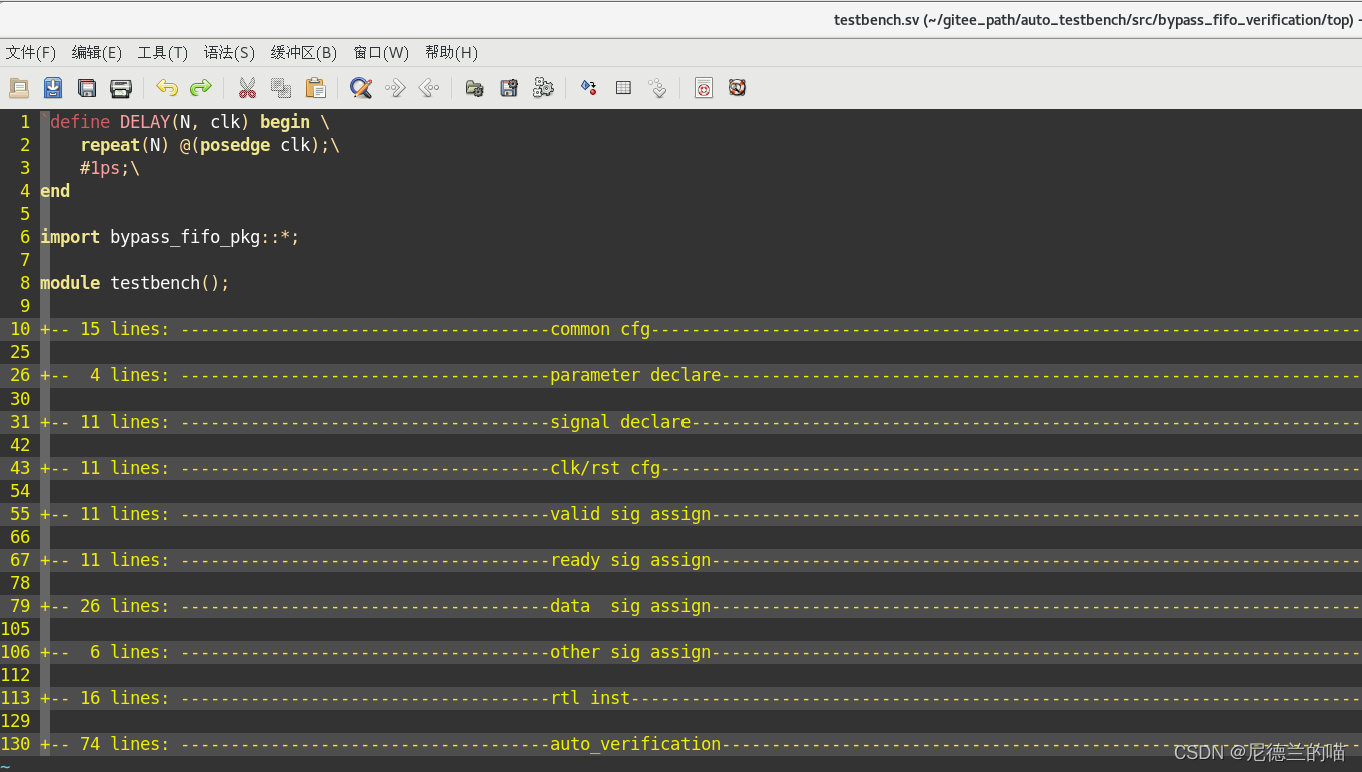

【芯片前端】auto_testbench的大版本升级——加入简单预期与自动比对

前言

前文提要:

【芯片前端】一键生成简易版本定向RTL验证环境的脚本——auto_verification_rtl脚本_尼德兰的喵的博客-CSDN博客

【芯片前端】可能是定向验证的巅峰之作——auto_testbench_autotestbench_尼德兰的喵的博客-CSDN博客

工具路径:

auto…

【HISI IC萌新虚拟项目】spt_core模块方案文档

spt_core为实现包转发功能的模块,为spt模块的核心部分。spt还包含test_core和spt_core访问sram的分发功能。该文档仅为参考 spt_core模块概述

spt_core需要实现的功能如下: 1 、根据头域 (Header) 指示,开始一包的接收;2 、净荷内容进行字节序的转换,高位字节放低位,低位…

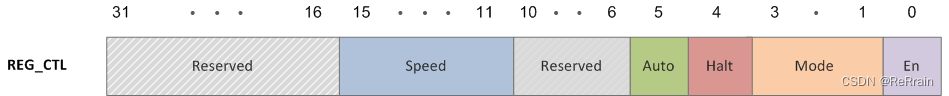

【HISI IC萌新虚拟项目】test_core模块方案文档

该文档为test_core spec,仅为参考,如果在进行本系列虚拟项目的学习与实践,请自行完成本部分内容。 1.Introduction

用于对 SRAM 实现自动的可配置地址线、数据线故障检测。

1.CPU 控制

CPU 向芯片的工作模式选择寄存器写入0xXXXX_XX55后,芯片进入扫描工作模式, 并启动…

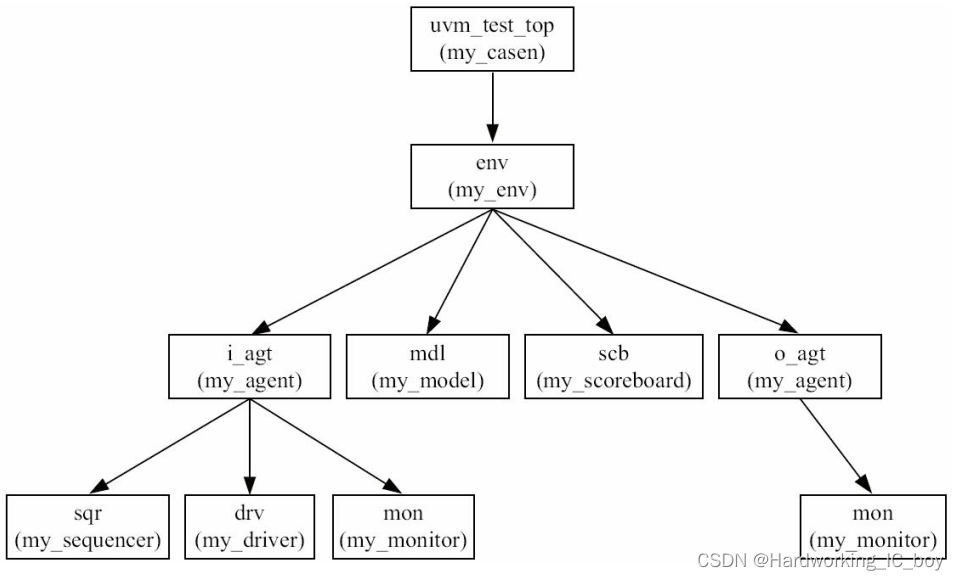

诙谐有趣的《UVM实战》笔记——第二章 一个简单的UVM验证平台

前言

某天白天在地铁上听鬼故事,结果晚上要睡觉时,故事里的情节都历历在目,给我鸡皮疙瘩起的~ 不过我倒是没有吓得睡不着,而是转念一想,为啥我学知识忘得很快,随便听的鬼故事却记得这么清楚咧?…

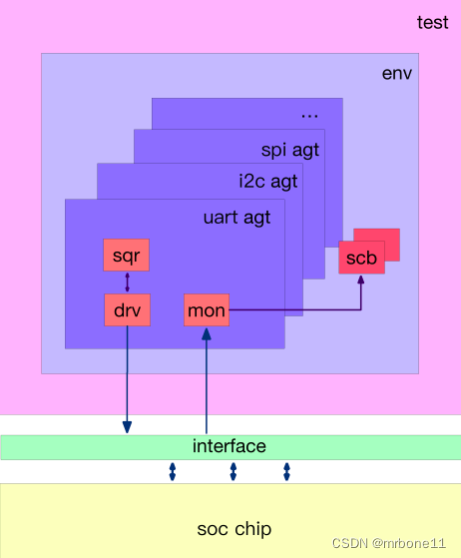

SV(UVM)实现多phase pipeline driver建模

在平台的搭建中,需要关注的重点一是平台的结构,怎么样便于复用,怎么样便于使用,不需要知道内部层次结构就可以很好的配置和使用。另一点就是实现了,驱动怎么实现?monitor怎么实现?sequence怎么实…

uvm白皮书练习_ch2_ch224_加入virtual interface

记录

参考使用uvm白皮书内容

从根本上来说,应该杜绝在验证平台中使用绝对路径

避免绝对路径一个方法是使用宏

define TOP top_tb

define TOP top_tb

task my_driver::main_phase(uvm_phase phase);phase.raise_objection(this);uvm_info("my_driver"…

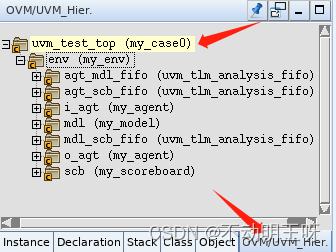

verdi显示OVM/UVM Hierarchy View

verdi显示OVM/UVM Hierarchy View 背景 使用vcsverdiUVM进行UVM debug的时候,verdi加载的时候看不到UVM树形结构图 解决办法 simv UVM_VERDI_TRACE“UVM_AWAREHIER” -guiverdi

2023-10-9 打开界面后,并不会直接显示树形层级 需要先仿真一定时间&#x…

【从零开始学习 UVM】10.5、UVM TLM —— UVM TLM Blocking Get Port

文章目录 UVM TLM Get Port Example1. 创建一个发送方类,其端口类型为 uvm_blocking_get_imp3. 创建接收器类,等待 get 方法。4. 在更高层次上连接端口及其实现Get端口阻塞行为任何组件都可以通过 TLM get 端口请求从另一个组件接收事务。发送组件应定义获取端口的实现。该实…

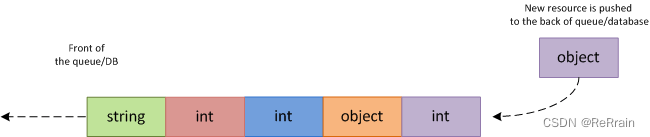

【从零开始学习 UVM】9.1、UVM Config DB —— UVM Resource database 资源库详解

文章目录 resource 是一个参数化的容器,可以保存任意数据。资源可用于配置组件、为序列提供数据或在TestBench不同部分之间启用信息共享。它们使用作用域信息(scope)存储,因此其可见性可以限制在TestBench的某些部分中。您可以将任何数据类型放入资源数据库中,并使另一个组…

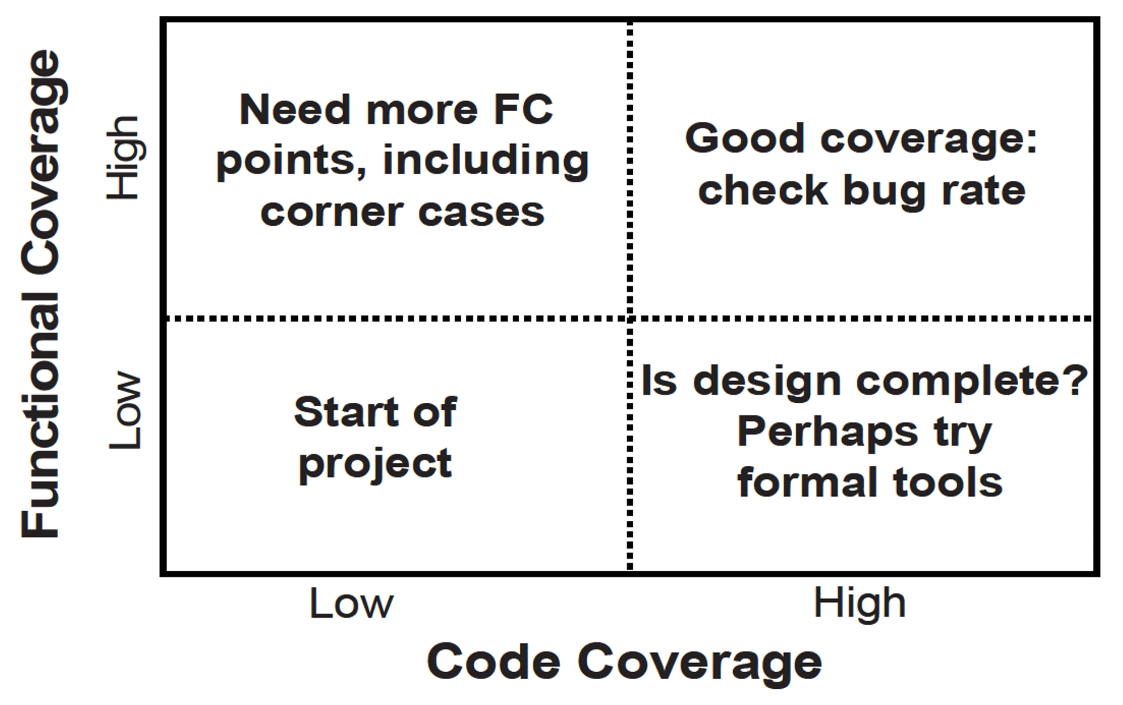

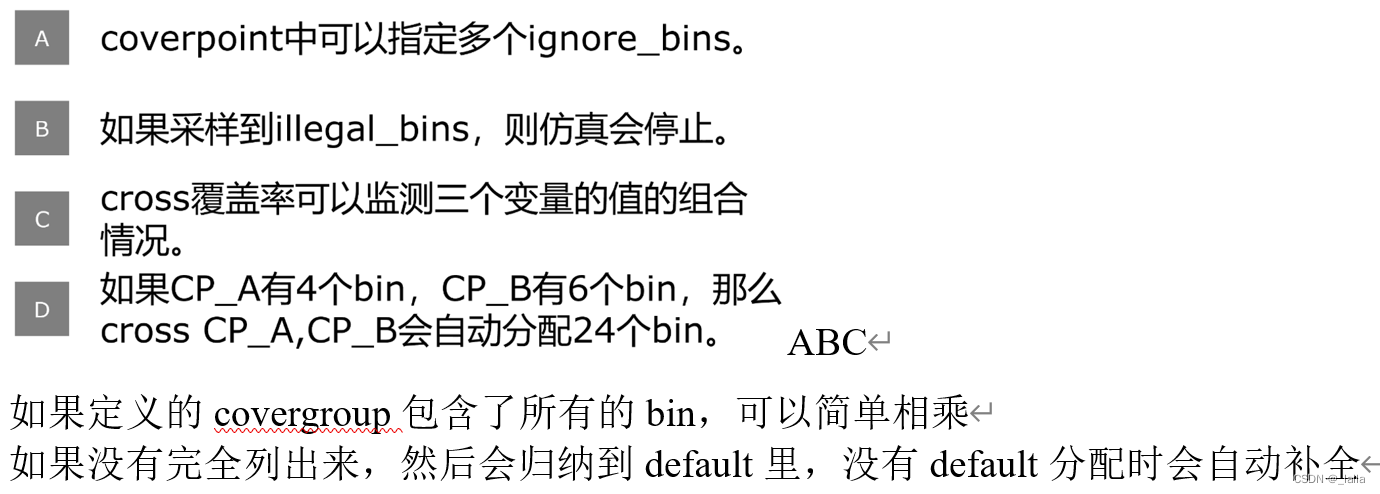

UVM学习笔记2——验证基础知识(验证计划、验证方法)

文章目录前言一、覆盖率二、验证计划1、验证计划模板2、验证计划评估三、验证方法1、动态仿真/dynamic simulation2、静态检查/formal check3、虚拟模型4、硬件加速/hardware acceleration5、效能验证6、性能验证四、验证分类1、验证工具2、验证复杂度/可见度/透明度3、验证的芯…

uvm_config_db性能权衡

根据mentor的推荐,尽量少用uvm_config_db,因为uvm_config_db是一个数据库,使用正则表达式匹配所有结果,如果数据库过大会影响验证平台性能。但是同时也提到性能与方法学乃至OOP有一个trade off.

这里几个减少uvm_config_db的方法:…

【从零开始学习 UVM】11.1、UVM Register Layer —— Register Layer 概述

文章目录 什么是UVM寄存器层(Register Layer)?寄存器是什么?什么是寄存器块(register block)?什么是内存映射(memory map)?什么是UVM寄存器层(Register Layer)?

UVM寄存器层类用于在待验证设计(DUV)中创建内存映射寄存器(memory-mapped registers)和内存(memo…

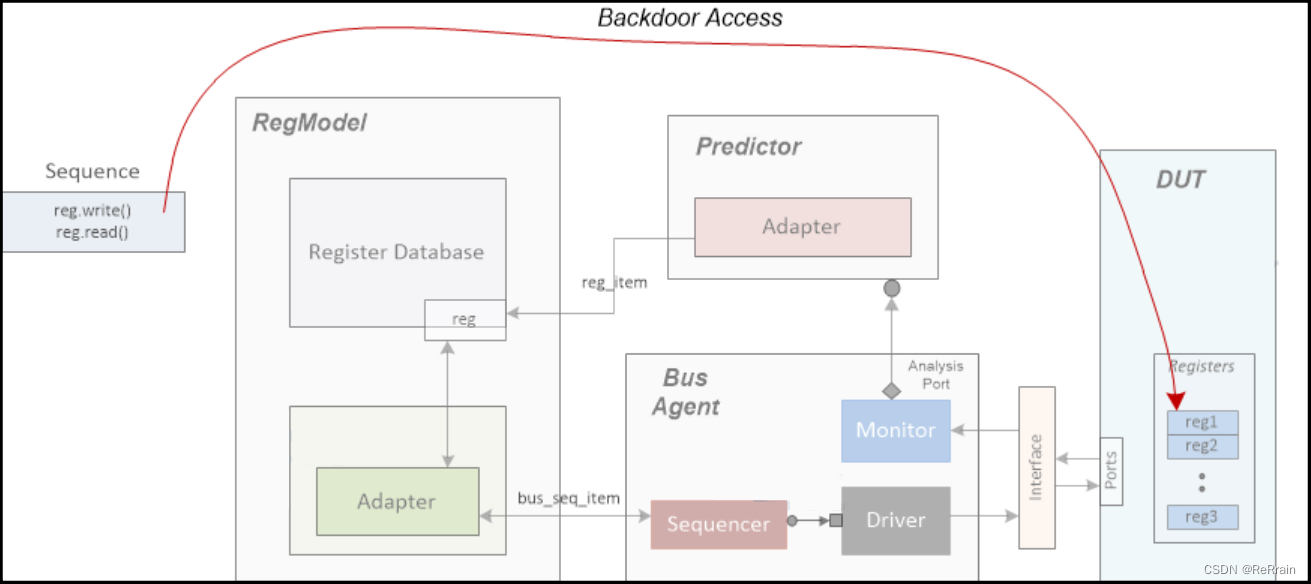

【从零开始学习 UVM】11.3、UVM Register Layer —— UVM Register Environment

文章目录 Register AdapterRegister Predictor创建一个Predictor的步骤1. 声明一个带参数的寄存器预测器版本,与目标总线事务类型一致2. 在注册环境中构建预测器3. 将寄存器映射、适配器和分析端口连接到预测器。Register 环境集成连接寄存器env在上一节寄存器模型(Register …

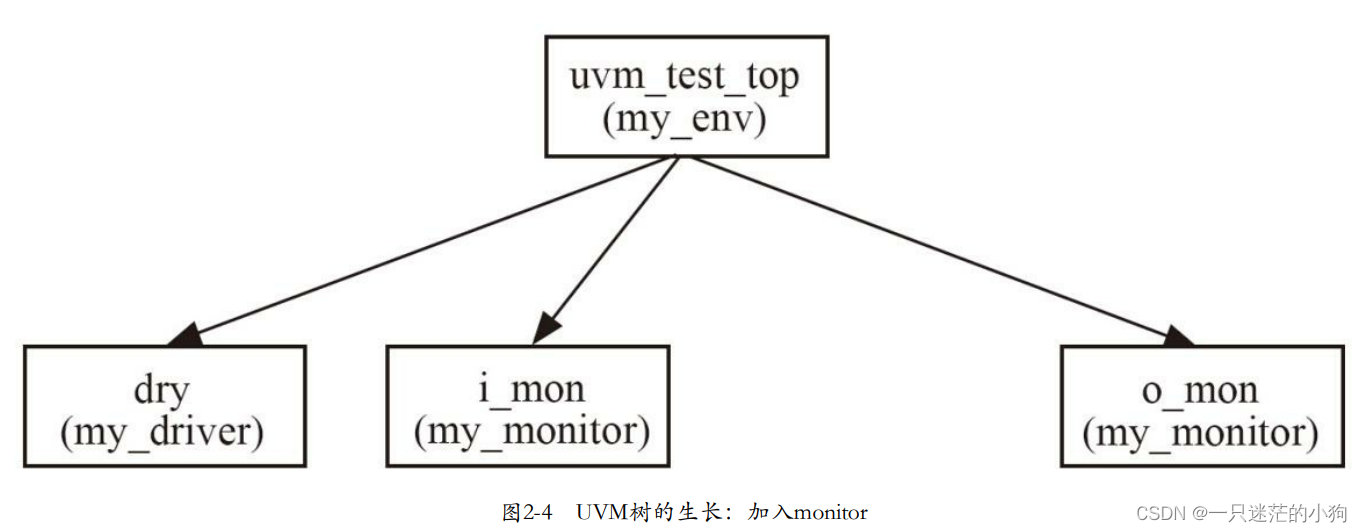

UVM验证环境中加入monitor

验证平台必须监测DUT的行为,只有知道DUT的输入输出信号变化之后,才能根据这些信号变化来判定DUT的行为是否正 确。 验证平台中实现监测DUT行为的组件是monitor。 driver负责把transaction级别的数据转变成DUT的端口级别,并驱动给DUT&…

uvm_config_db使用注意

uvm_config_db将数据存入数据库中供set, get, 注意这里存进去了就是一个半全局的变量,如果有一处改变了就会对其他使用了相同值的变量造成影响,和全局变量效果是一样的。因此

1. 在对要传递的对象配置完毕后,尽量单向使用uvm_config_db get到…

支持寄存器模型读写功能的AHB driver实现——导读

1.前言

UVM driver在接口协议的实现中起着非常重要的作用,因为它一端处理基于类的事务级sequence,另一端处理基于时钟的信号/引脚级的总线行为。因此,如何实现 UVM driver及其与sequence的同步对于 DUT 和 UVM 环境之间的交互以及避免 UVM d…

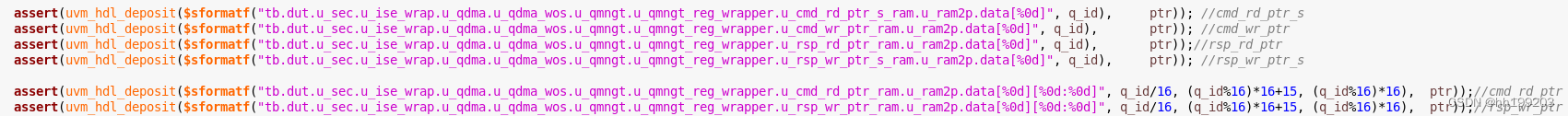

记录一些uvm自带的后门访问方法

文章目录前言一、uvm后门访问方法1、 int uvm_hdl_check_path(string path)2、int uvm_hdl_deposit(string path, uvm_hdl_data_t value)3、int uvm_hdl_force(string path, uvm_hdl_data_t value)4、int uvm_hdl_release(string path)5、int uvm_hdl_read(string path, output…

UVM中的config_db机制传递interface

(1)定义interface

interface my_if(input clk, input rst_n);logic [7:0] data;logic valid;endinterface

(2)在tb中使用interface 定义了interface后,在top_tb中实例化DUT时,就可以直接使用。 先…

【从零开始学习 UVM】11.5、UVM Register Layer —— 后门访问 实战项目(RAL实战,交通灯为例)

文章目录 后门访问是什么?定义后门 HDL 路径示例sequence中的后门访问示例UVM寄存器模型允许使用前门访问DUT寄存器,就像我们之前在寄存器环境中看到的那样。

这意味着环境中的所有寄存器读写操作都会转换为总线事务,并驱动到设计的总线接口,就像典型系统中的任何其他硬件…

Cadence Xrun UVM Makefile

#记录工作实践

#基于Cadence Xrun工具的UVM Makefile

# #-- #-- File name : Makefile #-- Author : sh

#-- Date : 2023/11/01

#-- Abstract : Cadence Xcelium Xrun Makefile #-- # #############################################…

如何使用UVM寄存器模型中的callback

文章目录 前言一、底层UVM的介绍二、UVM寄存器模型callback的使用1、拓展2、绑定 总结 前言

我们在使用UVM的寄存器模型过程中,有时候需要在寄存器配置配置前准备一些数据,或者在寄存器配置之后触发一些操作,这个时候就可以用到UVM寄存器模型…

uvm中transaction的response和id的解读

在公司写代码的时候发现前辈有一段这样的代码:

....//其他transaction

uvm_create(trans);........

uvm_send(trans);

tmp_id trans.get_transaction_id();

get_response(rsp,tmp_id);

如果前面有其他transaction,这段代码里的get_response不带id的话…

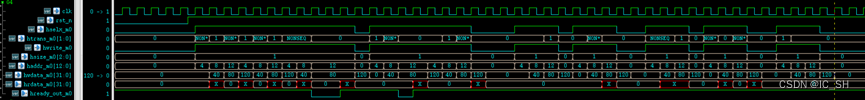

UVM项目笔记——通过寄存器模型实现AHB接口的寄存器读写(内含源码)

目录 1.前言

2.DRIVER实现

2.1 AHB二级流水时序

2.2 “队列错位法”实现driver

2.3 driver代码

2.4 仿真log与波形

2.5 多级流水拓展方法 1.前言

UVM driver在接口协议的实现中起着非常重要的作用,因为它一端处理基于类的事务级sequence,另一端处…

uvm白皮书练习_ch2_ch223_加入objection机制

UVM中通过objection机制来控制验证平台的关闭。 在每个phase中,UVM会检查是否有objection被提起(raise_ objection),如果有,那么等待这个objection被撤销(drop_objection)后停止仿真;…

【从零开始学习 UVM】2.6、UVM 基础功能 —— UVM Object Pack/Unpack

UVM自动化宏还包括将类变量打包(pack)成位或字节流的机制,以及解包(unpack)缩位流并填充类内容。在处理SPI、I2C和RS-232等串行通信形式时,这特别有用。 文章目录三种 pack/unpack 方法介绍使用自动化宏pac…

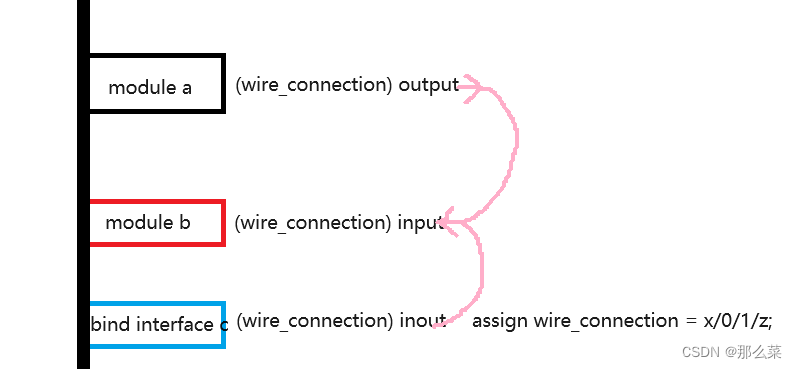

UVM 验证方法学之interface学习系列文章(八)《interface不小心引入X态问题》

前面的文章学习,想必大家都对interface 有了深入了解。大家可不要骄傲哦,俗话说:小心驶得万年船。今天,再给大家介绍一个工作中,不是经常遇到,但是一旦遇到,会让你纠结很久的事情。

前面文章提到,随着验证复杂度的不断增加,interface 的bind 的操作,是必不可少的用法…

IC验证工程师工作一周年的体会

转眼之间自己已经工作一周年了,作为一名验证工程师,这一年里面感觉自己虽然有了一定的成长,但是成长的还是比较缓慢的,接下来从个人的角度说说我现在对从IC验证的一些体会。 一.要养成良好的工作习惯 (1)自…

UVM中uvm_config_db机制背后的大功臣

1. 前言

本次讲一下UVM中的uvm_config_db,在UVM中提供了一个内部数据库,可以在其中存储给定名称下的值,之后可以由其它TB组件去检索。这样的数据库允许我们以不同的名称存储不同的配置设置,这些配置可以在需要时潜在地配置TB组件…

UVM产生异常激励的方法

在UVM中,产生异常激励的方法(以白皮书中源码为例) 在my_transaction中添加一个crc_err的标志位这样,在post_randomize中计算CRC前先检查一下crc_err字段,如果为1,那么直接使用随机值,否则使用真…

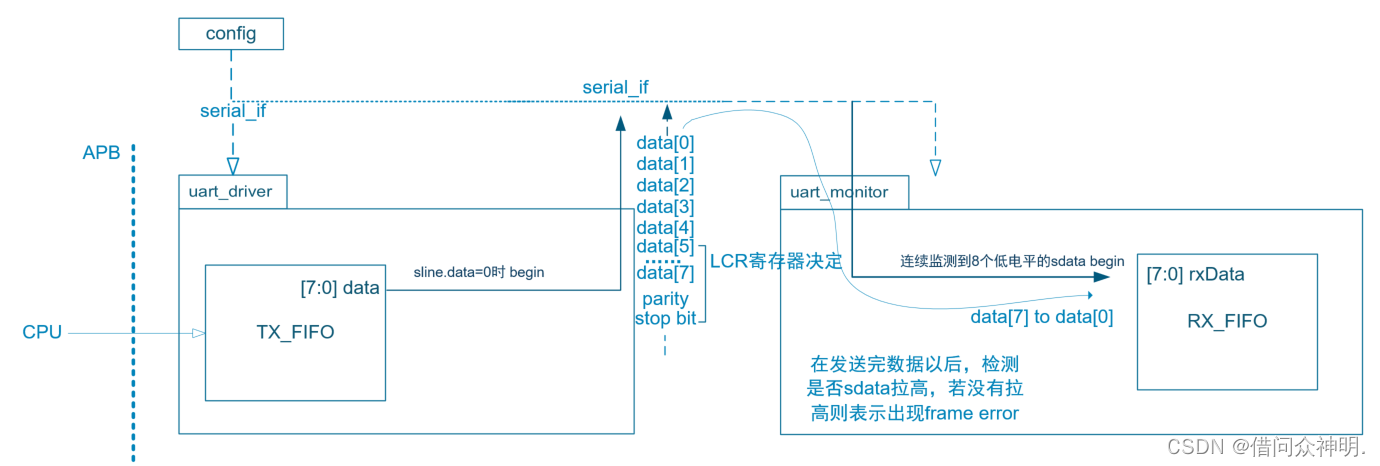

driver与monitor间的数据传输--UART

文章目录uart发送数据(driver)uart接受数据(monitor)uart发送数据(driver)

CPU通过APB总线给uart写入数据,将数据保存在TX_FIFO中,然后通过uart_driver将并行数据串行的发送到总线上。注意:发送…

UVM中保存指定ID或report severity为log文件的方法

当然可以尝试grep,如果两者都要筛选可以用更复杂的语法。这里只讨论UVM原生的处理方法。 那就是使用set_report_severity_*_hier系列方法,不带hier的版本对本模块有效,如果希望对子模块有效就得用hierarchy系列。几点注意事项: 1.set系列函数…

uvm的factory机制

factory机制的作用:自动创建一个类的实例并调用其中的函数(function)和任务 (task)。

class my_driver extends uvm_driver;uvm_component_utils(my_driver)function new(string name "my_driver", uvm_co…

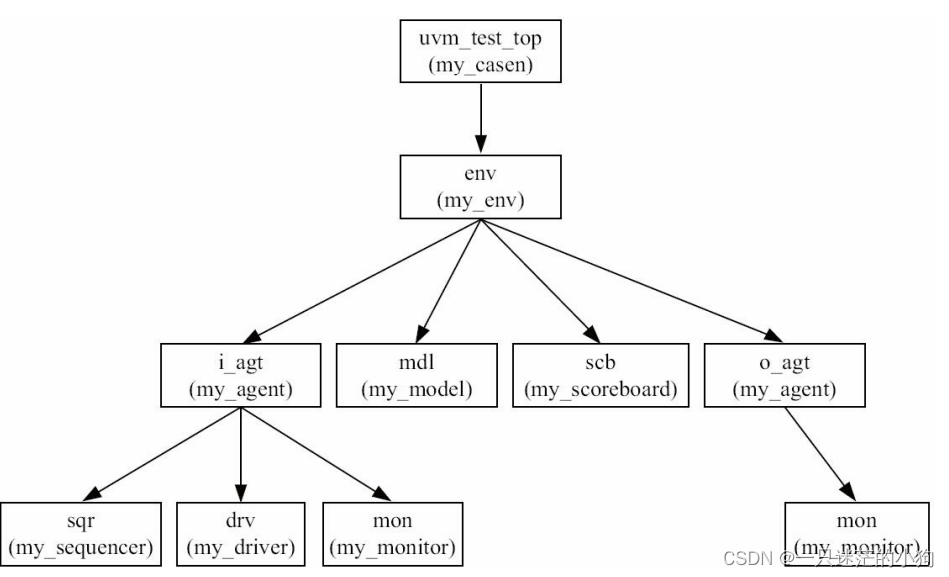

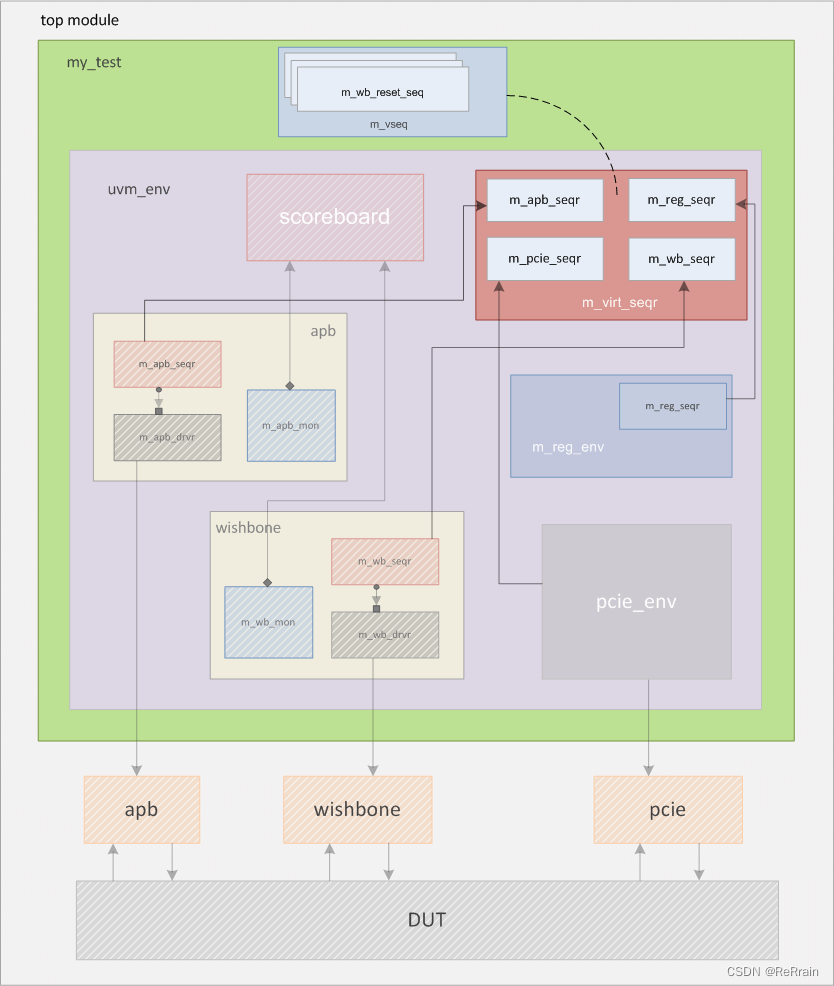

第十二段:基于env的重用

现代芯片的验证通常分为两个层次, 一是模块级别( block level, 也称为IP级别、 unit级别) 验证, 二是芯片级别( 也称为SOC级别) 验证。 一个大的芯片在开发时, 是分成多个小的模块来…

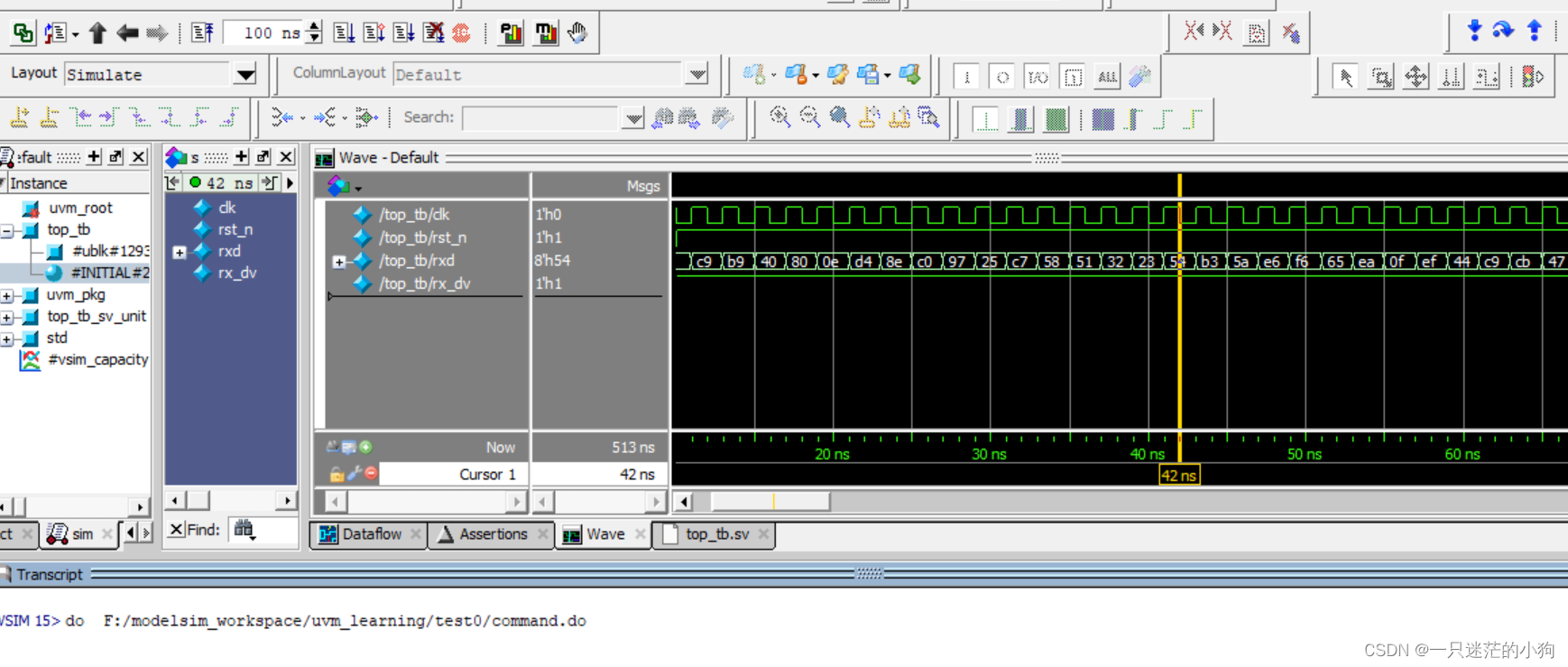

uvm白皮书练习_ch2_ch221只有driver的验证平台之*2.2.1 最简单的验证平台

uvm白皮书练习 ch221 dut.sv 这个DUT的功能非常简单,通过rxd接收数据,再通过txd发送出去。其中rx_dv是接收的数据有效指示,tx_en是发送的数据有效指示。

module dut (clk,rst_n,rxd,rx_dv,txd,tx_en

);input clk ; input rst_n ; in…

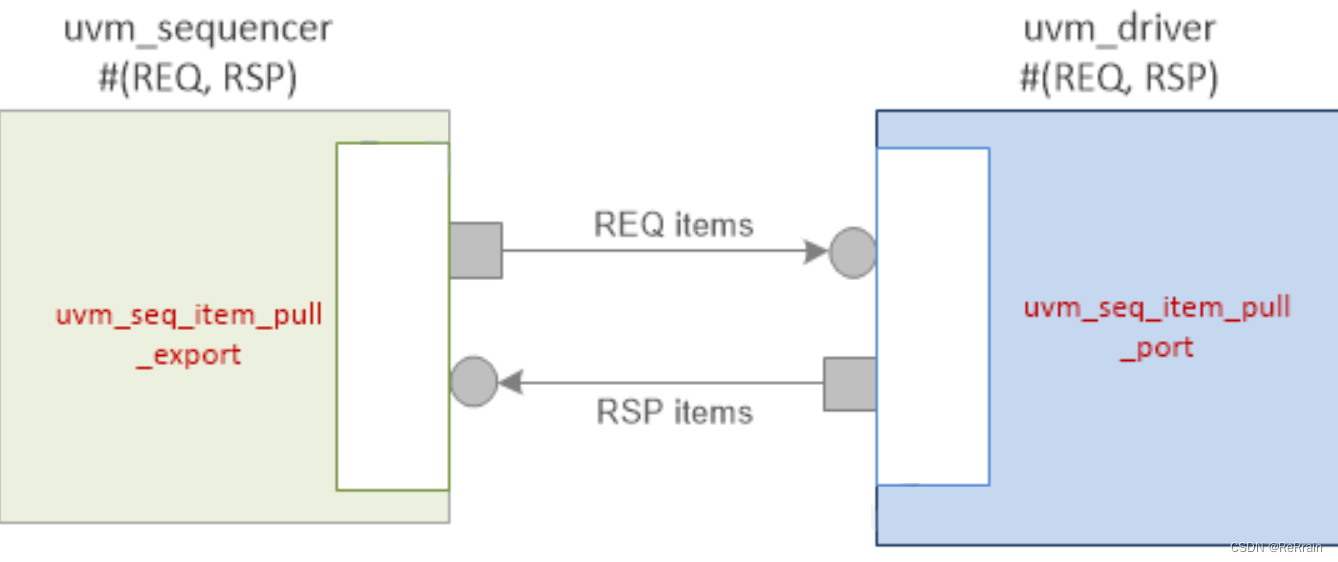

【从零开始学习 UVM】7.1、Driver Sequencer Handshake —— Driver 与 Sequencer 的握手机制

文章目录 sequencer如何与driver通信?为什么我们需要driver sequencer API 方法?driver中的TLM port叫什么?sequencer中的TLM port叫什么?一个driver如何连接到sequencer?sequencer如何与driver通信?

driver类包含一个名为uvm_seq_item_pull_port的TLM端口,该端口连接到…

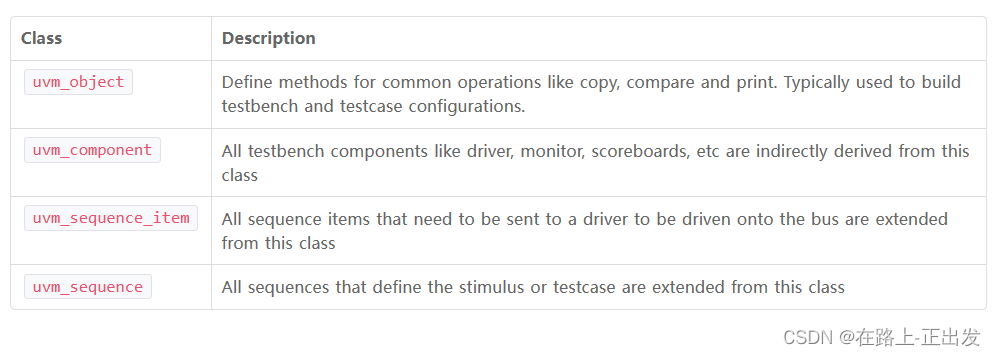

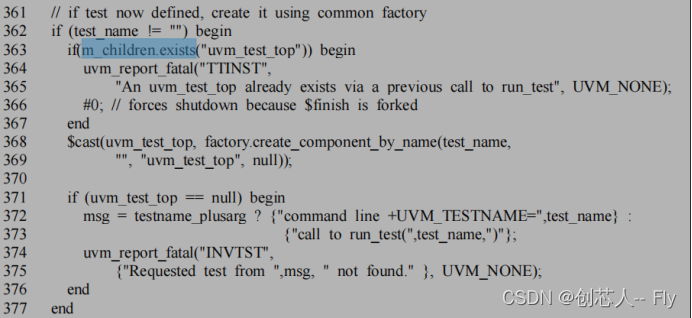

UVM源码--uvm_component 浅析(一)

目录

1. uvm_object

2. uvm_component

3. 为什么在uvm_component 例化是需要指定一个parent?

4.uvm_component 的树形结构是如何组织起来的?

5. 静态函数与非静态函数的区别: 6. uvm_root 的单实例实现思路:

7. run_test 的…

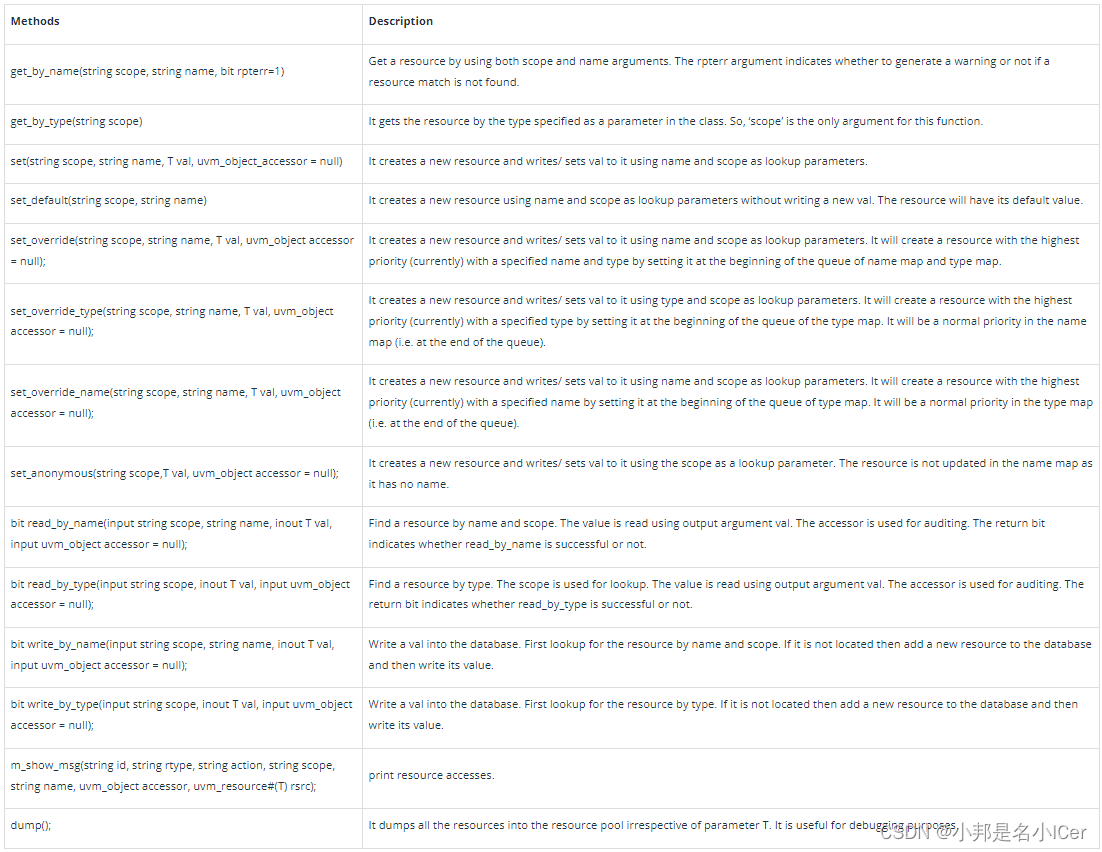

7.2 uvm_resource_db in UVM

uvm_resource_db是一个类型参数化 type-parameterized的类,它是资源数据库顶部的一个方便层(convenience layer)。这个便利层简化了对低级数据库的访问,并且没有添加新功能。因此,uvm_resource_db不是从uvm_resource类派生的。以下uvm_resour…

【从零开始学习 UVM】6.5、UVM 激励产生 —— UVM Virtual Sequence【重要】

文章目录 使用virtual sequencer不使用virtual sequencervirtual sequence是一个容器,用于在环境中的virtual sequencer上启动多个sequence。

这个virtual sequence通常由一个具有对真实sequencers句柄的virtual sequencers执行。

需要virtual sequence的原因是当您需要在不…

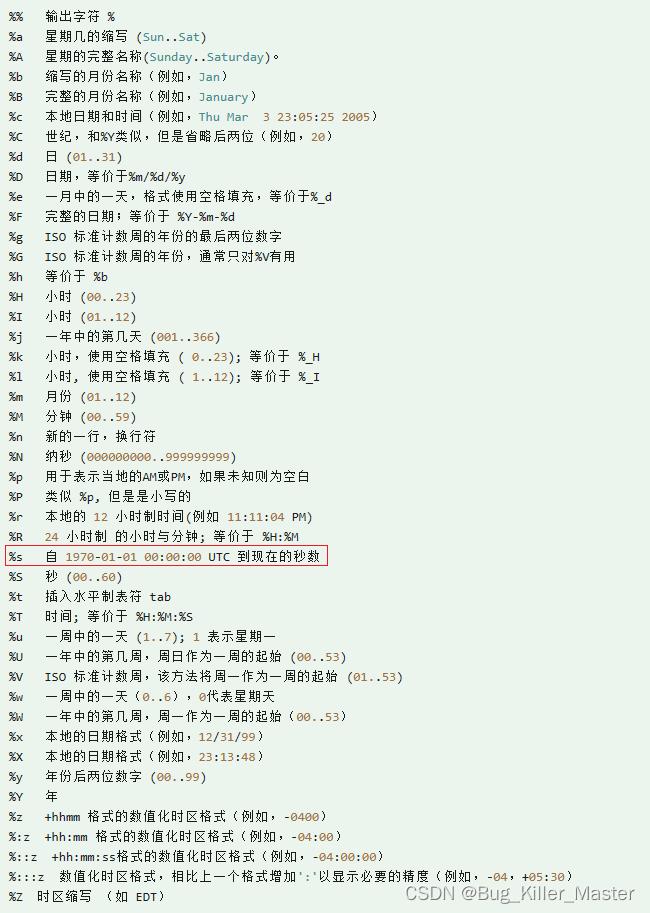

uvm环境获取系统时间的方法和使用案例

背景: 有时候我们想统计一下验证环境中某个步骤总共花费了多少时间,有什么比较方便的方法呢,利用$realtime理论上也是能做到的,不过这个和timescale绑定起来了,需要手动换算成单位是秒的数,现在提供一种利用…

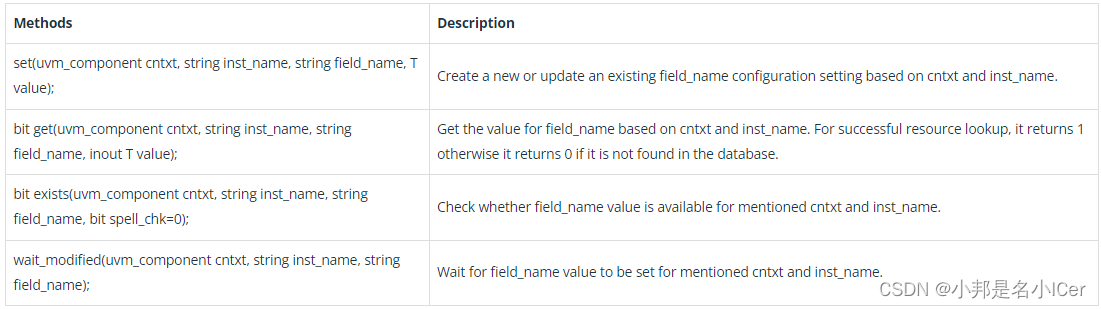

7.3 uvm_config_db in UVM

uvm_config_db类派生自uvm_resource_db类。它是uvm_resource_db顶部的另一层便利层,简化了用于uvm_component实例的基本接口(资源库的访问方法)。

下面uvm_config_db类的代码段取自uvm源代码。

class uvm_config_db#(type Tint) extends uv…

Sequence的启动

Sequence的启动1.手动启动2.自动启动1.手动启动

在某个component(例如my_sequencer、my_env)的main_phase中手工启动sequence: task my_sequencer::main_phase(uvm_phase phase);my_sequence seq;phase.raise_objection(this);seqmy_sequence::type_id::create(&…

HLS 三角函数报错:undefined reference to ‘cordic_apfixed::circ_table_arctan_128‘

最近在通过HLS实现一些算法,其中用到了hls::cos函数,写完代码编译报错:

../Vitis_HLS/hls_cordic_apfixed.h:229: undefined reference to cordic_apfixed::circ_table_arctan_128

build/xf_computePhaseMap_accel.o: In function void cord…

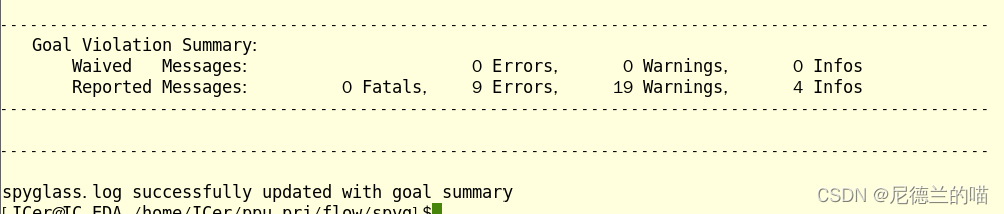

【HISI IC萌新虚拟项目】ppu模块基于spyglass的lint清理环境搭建与lint清理

关于整个虚拟项目,请参考: 【HISI IC萌新虚拟项目】Package Process Unit项目全流程目录_尼德兰的喵的博客-CSDN博客 前言

RTL代码在交付给验证同时进行功能验证时,可以同步进行lint的清理工作。一般而言影响编译和仿真的问题会在vcs的error和warning中被修正,因此清理lin…

【HISI IC萌新虚拟项目】Package Process Unit模块整体方案·PART2

4.系统功能和主要技术指标论证 4.1芯片总体结构图 芯片总体结构框图如图2所示。 图 2 packet_process_unit 芯片结构框图 芯片内部主要电路包括 cpu_if 接口电路、sram 检测电路 test_core 以及 spt 包转发接口电 路。以下对主要部分分别进行简要介绍:

1.cpu_if 接口电路

该…

uvm白皮书练习_ch2_ch231_加入transaction

2.3 为验证平平台加入各种组件 uvm白皮书练习_ch2_ch231_加入transaction

代码部分

top_tb.sv

timescale 1ns / 1ps

include "uvm_macros.svh"import uvm_pkg::*;

/*只能现在*/include "my_if.sv"

include "my_transaction.sv"

include "…

Win11+Modelsim SE-64 10.6d搭建UVM环境

1、添加源文件及tb文件

在目录下建立文件夹,将DUT和Testbench添加进去,文件夹内容如下所示:

2、以《UVM实战》中的例子做简单的示例:

2.1 设计文件 :dut.sv 功能很简单,即将接受到的数据原封不动发送出去…

【从零开始学习 UVM】3.7、UVM TestBench架构 —— UVM Monitor [uvm_monitor]

文章目录 什么是 monitor ?UVM monitor是做什么的?创建UVM monitor的步骤什么是 monitor ?

一个 UVM monitor 负责从设计接口捕获信号活动,并将其转换为可发送到其他组件的事务级数据对象。为了做到这一点,它需要以下内容: 虚拟接口句柄来处理此monitor尝试监视的实际接…

【从零开始学习 UVM】12.3、UVM RAL(续更) —— RAL Classes Methods

文章目录 uvm_reg_blockuvm_reg_block methodsuvm_reguvm_reg methodsuvm_reg_fielduvm_reg_field 访问策略uvm_reg_field methodsuvm_reg_fileuvm_reg_file methodsuvm_memuvm_mem methodsuvm_reg_mapuvm_reg_map methods设置单个map的相关sequencer和ada

[UVM]uvm_config_db和uvm_resource_db的区别

uvm_config_db和uvm_resource_db的区别 Q1:uvm_config_db和uvm_resource_db的区别 A:uvm_resource_db可以通过静态方法set()和read_by_name()完成对某个scopname的变量的配置和读取,但他与验证环境的层次没有关系。 A:实际上&…

UVM结构篇之八大组件功能概述

UVM是一种统一的验证方法,它是至关重要的,有不少人往IC验证方向发展的,多多少少都会去了解UVM。对于验证工程师来说,掌握UVM可以大大减轻验证工程师跨公司、跨项目工作的难度。

UVM

通用验证方法学(Universal Verifi…

UVM-什么是UVM方法学

概念简介

百度对UVM的解释如下: 通用验证方法学(Universal Verification Methodology, UVM)是一个以SystemVerilog类库为主体的验证平台开发框架,验证工程师可以利用其可重用组件构建具有标准化层次结构和接口的功能验证环境 UVM…

#UVM# 搞清验证平台中的 uvm_top 和 null ,不清不白!

目录

一 前言

二 正题

2.1 问题背景

2.2 惹是生非

2.3 刨根问底

三 总结 一 前言

记得很久之前,粗略的写过一篇文章《#UVM#

《UVM实战》学习笔记——第七章 UVM中的寄存器模型1——寄存器模型介绍、前门/后门访问

文章目录 前言一、寄存器模型简介1.1 带寄存器配置总线的DUT1.2 参考模型如何读取寄存器的值1.3 寄存器模型的基本概念 二、简单的寄存器模型2.1 只有一个寄存器的寄存器模型2.2 将寄存器模型集成到验证平台2.3 在验证平台中使用寄存器模型 三、前门访问和后门访问3.1 前门访问…

uvm白皮书练习_ch2_ch222加入factory机制

uvm白皮书练习_ch2_ch222只有factory机制 factory机制的实现被集成在了一个宏中:uvm_component_utils。 这个宏所做的事情非常多,其中之一就是将my_driver登记在UVM内部的一张表中,这张表是factory功能实现的基础。

自动创建一个类的实例并调…

UVM实战:一个component内有多个IMP

对于一个 analysis_imp来说,必须在其实例化的uvm_component中定义一个write的函数。但在 现实情况中,scoreboard除了接收monitor的数据之外,还要接收reference model的数据。相应的scoreboard就要再添加一个 uvm_analysis_imp的IMP࿰…

在UVM验证平台加入transaction

transaction是一个抽象的概念。一般来说,物理协议中的数据交换都是以帧或者包为单位的,通常在一帧或者一个包中要定义 好各项参数,每个包的大小不一样。很少会有协议是以bit或者byte为单位来进行数据交换的。transaction就是用于模拟这种实际…

【从零开始学习 UVM】12.6、UVM RAL(续更) —— RAL Predictor

文章目录 隐式(自动)预测显式预测在TestBench环境中的插件reg_predictor被动预测UVM RAL 预测器是一个组件,它基于物理接口上的transaction更新镜像值,UVM 提供了“uvm_reg_predictor”基类。

DUT 寄存器可以通过 RAL 方法(如读取和写入)或在目标agent上运行具有有效地址…

【从零开始学习 UVM】12.8、UVM RAL(续更) —— UVM RAL Model 实战项目(基于AXI总线的寄存器读写实例)

让我们了解寄存器模型是如何构建的,将其与验证环境集成,并使用读写方法访问DUT寄存器。 文章目录 1.1 R寄存器描述1.2 Testbench Block 图1.3 Testbench hierarchy1.4 总体步骤1.4.1 步骤1:创建注册(RAL)模型的步骤1.4.1.1 Step A: 编写寄存器类1.4.1.2 Step B: 编写寄存器…

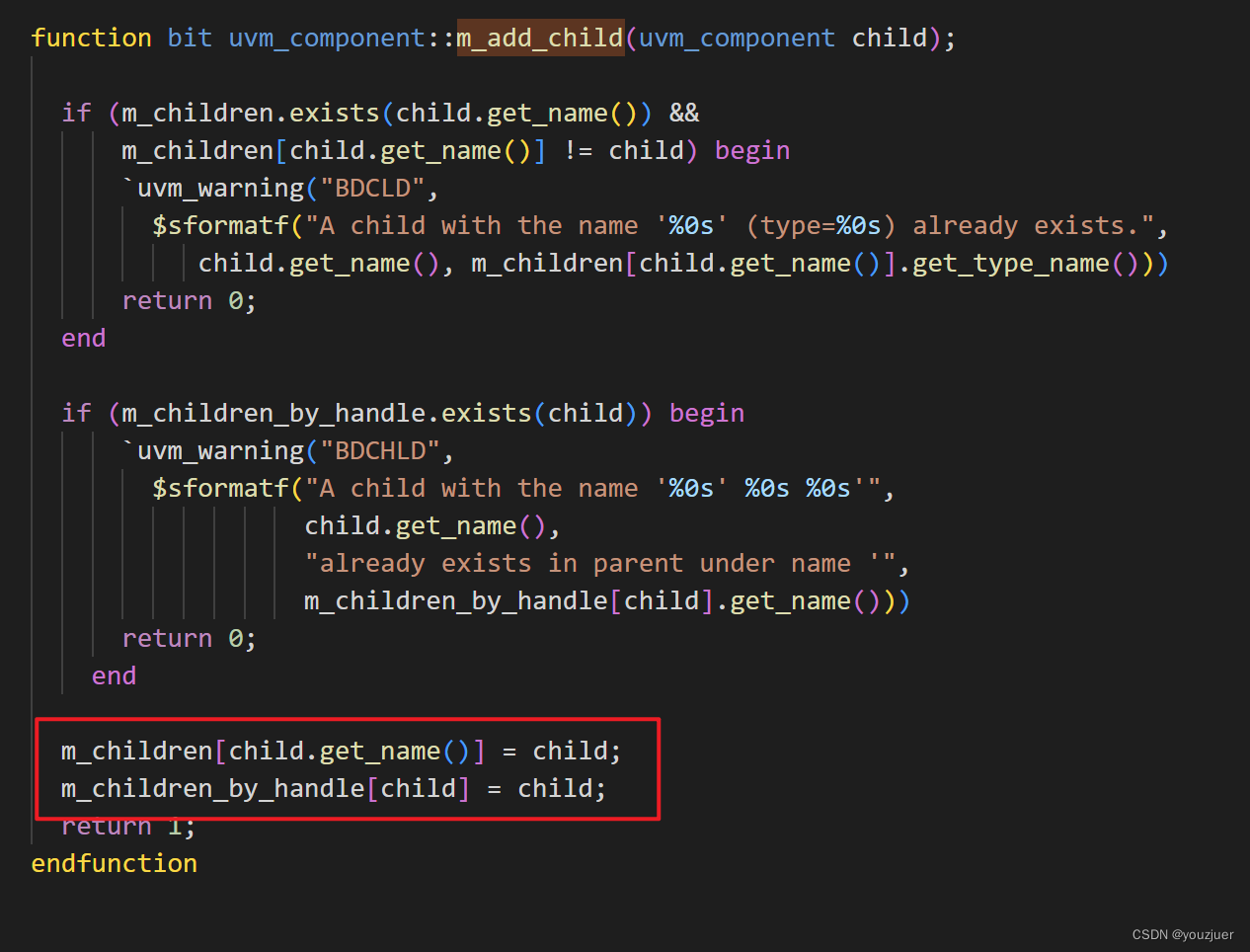

uvm_component源码解析

一、为什么在实例化comonent的时候要指定一个parent

答:为了构成树状结构,方便以后的组件遍历

具体解释:

为了遍历, 二、代码分析

2.1

为了实现上述的功能,需要下面的两个联合数组 这个父指针就是m_parent 2.2 我们只关注红框部分,

<

【从零开始学习 UVM】10.7、UVM TLM —— TLM Fifo [uvm_tlm_fifo]

文章目录 UVM TLM FIFO Example1. 创建一个发送器类,其端口类型为 `uvm_blocking_put_port`2. 创建接收器类,使用 get 方法进行接收。3. 通过高层次的 TLM FIFO 连接这两个组件假设发送方的数据速率比接收方获取数据包的速率快得多。需要在两者之间插入一个FIFO元素来存储数据…

【从零开始学习 UVM】8.2、Reporting Infrastructure —— uvm_printer 详解

文章目录 老派风格在UVM中如何完成uvm 风格Table printerTree printerLine printerprint使用print使用条件使用konb更改print配置示例在一个随机验证环境中,数据对象不断地由不同的组件生成和操作,如果能够显示对象的内容,则调试会变得更加容易。

老派风格

传统上,这是通…

#UVM# 搞清验证平台中的 uvm_top 和 null ,不清不白?

目录

一 前言

二 正题

2.1 问题背景

2.2 惹是生非

2.3 刨根问底

三 总结 一 前言

记得很久之前,粗略的写过一篇文章《#UVM#

【从零开始学习 UVM】3.8、UVM TestBench架构 —— UVM Agent [uvm_agent]

文章目录 什么是 UVM Agent?所有的Agent Type是什么?如何确定UVM Agent是主动还是被动的?创建UVM代理的步骤一个UVM代理做什么?如何将UVM代理配置为主动或被动?一个UVM Agent例子推荐做法什么是 UVM Agent?

一个 Agent 将Sequencer、Driver和Monitor封装成一个单一实体,…

uvm_declare_p_sequencer获取sequencer原理

在看张强白皮书P189中对uvm_declare_p_sequencer的描述时有一个疑问,就是为什么通过sequencer的类名就能获取到sequencer,然后自己下来查了一下,理了一下关系才明白。

首先就是uvm_declare_p_sequencer这个宏,看了一下定义的地方…

【从零开始学习 UVM】3.5、UVM TestBench架构 —— UVM Sequencer [uvm_sequencer]

文章目录 Usage(用法)Custom Sequencer(自定义sequencer)Class Hierarchy一个 sequencer 生成数据事务作为类对象并将其发送到driver以执行。建议扩展uvm_sequencer基类,因为它包含了允许sequence与driver通信所需的所有功能。基类是由可以被sequencer处理的requset和resp…

UVM Heartbeat机制

1. 前言

在硬件电路中,为了使系统在异常情况下能自动复位,一般都需要引入看门狗(Watchdog)。看门狗其实就是一个定时器电路。当看门狗启动后,计数器开始自动计数,经过一定时间,如果没有被清零,计数器溢出就…

![【从零开始学习 UVM】3.7、UVM TestBench架构 —— UVM Monitor [uvm_monitor]](https://img-blog.csdnimg.cn/195f597a6bbf4ea78fbacf540fed2476.png)

![【从零开始学习 UVM】10.7、UVM TLM —— TLM Fifo [uvm_tlm_fifo]](https://img-blog.csdnimg.cn/441de33cb39147a681d61705a3314fcc.png)